引言:隨著VoIP被廣泛整合進入WiFi中,實現(xiàn)成本、功耗和功能之間的平衡對設計提出了重大的挑戰(zhàn)。本文描述的具有DSP功能的嵌入式RISC處理器在不增加系統(tǒng)復雜性、對功耗影響很小的前提下,為移動電話增加WiFi電話功能提供了很好的解決方案。

WiFi電話(VoWiFi)的市場容量預測顯示,隨著消費者持續(xù)采用VoIP技術,WiFi電話的市場容量將大幅增長。這種預測結果引起了各地系統(tǒng)集成商和設計師的關注,許多設計公司爭相推出或研究新的解決方案以滿足這種即將到來的市場需求。雖然很容易發(fā)現(xiàn)WiFi電話解決方案的價值所在,但設計出能夠在成本、功耗和功能之間達到平衡的市場暢銷產(chǎn)品對現(xiàn)有公司和新進入的公司都提出了極大的挑戰(zhàn)。

隨著大眾普遍接受標準化信令格式-會話初始協(xié)議(SIP),以及免費易用的軟件電話包(如Skype)的出現(xiàn),VoIP電話通話逐漸變得流行起來。隨著WiFi手機、PDA和能夠在蜂窩和WiFi網(wǎng)絡間漫游的雙模WiFi/蜂窩手機中VoIP被整合進WiFi,VoIP正在進入無線應用。據(jù)市場調查公司In-Stat預測,雙模手機和WiFi單模手機的普通消費和商業(yè)應用總量在2009年將達到1.41億部。雖然這種應用是迄今為止VoIP的市場,但把VoIP整合到如汽車系統(tǒng)和便攜式媒體播放機(PMP)這樣的其它的功率有限設備里也會給半導體供應商帶來巨大的市場機遇。

毫無疑問,如今功能豐富的手機的發(fā)展在功率有限電子設備中一馬當先。的手機具有大屏幕LCD、照相機、藍牙和802.11b WiFi連接。用戶可以觀看或捕獲視頻、上網(wǎng)沖浪和檢查電子郵件。這種智能電話需要使用高容量的電池,電池容量可能比普通手機用的電池容量大三倍。但即使配備了高容量電池,在使用WiFi連接時其總的允許通話時間也會從典型的5小時左右下降至2小時不到。更糟的是,用戶必須采用成本大大增加、體積更大、更重的電池。而通常,電池使用時間和價格是消費者關注的因素。

在這些功率有限的電話設備中增加基于WiFi的VoIP功能需要增加支持802.11g WiFi、語音和IP網(wǎng)絡的軟硬件。雖然這聽起來微不足道,但802.11g的實現(xiàn)特別具有挑戰(zhàn)性,要知道典型的802.11g筆記本芯片組在傳輸時消耗的電流要比整個手機在通話期間消耗的電流還要高。典型的手機在通話時功耗約600mW,而標準的WiFi無線設備在收發(fā)時的功耗高達800mW。在基于WiFi的VoIP通話期間,處理器和其它邏輯電路還要消耗額外的功率,因此WiFi電話的總功耗很容易達到1W的范圍。通話期間功耗增加400mW大約會縮短一半的總體通話時間。

即使處理器并不是這種系統(tǒng)中耗電的器件,但為了降低整個系統(tǒng)功耗,也很有必要管理處理器的功率。電池技術的發(fā)展太慢,根本跟不上消費者對更長電池壽命和增強的功能的需求,因此處理器和系統(tǒng)電源的效率成為增加功能(此處為WiFi電話)可用的功率預算,并能夠在不降低用戶使用體驗的條件下實現(xiàn)創(chuàng)新服務的關鍵因素。對于支持VoIP的電池供電設備來說,在滿足用戶使用性能的前提下,處理器的選擇應該是能實現(xiàn)功耗和成本的內核。

VoIP的處理

包括雙模和WiFi電話手機在內的大多數(shù)VoIP終端都需要同時支持1~2路語音通道,這確保能滿足雙方和三方會議通話的需求。每路語音通道由用于編解碼的ITU(國際電信聯(lián)盟)G.7xx算法、語音質量(G.168-2000)和電話信令(SIP或H.323)組成。

一個VoIP設備必須支持多個編解碼類型,具體使用類型取決于各自的網(wǎng)絡要求。常用的編解碼標準有G.729AB、G.723.1、G.711和iLBC。語音質量組件包括聲學回聲消除(G.167 AEC)、語音活動檢測(VAD)和舒適噪聲產(chǎn)生(CNG)以及抖動緩沖:回聲消除用于濾除語音的回聲,VAD用來編碼和壓縮語句間的靜音,而CNG用來在電路或環(huán)境導致的噪聲情況下提供語音檢測。抖動緩沖可以確保不管經(jīng)過網(wǎng)絡的延時有多大,語音包括都能以正確的順序得到處理,同時使包的丟失少。其它組件還有像用于語音郵件和尋呼的雙音多頻(DTMF)信號系統(tǒng)撥號這樣的電話算法、基于SIP或H.323的通話建立控制。實際上,上述標準目前已經(jīng)很普遍,但任何VoIP應用都需要具備軟件可升級性,語音編解碼和通話控制標準還在不斷發(fā)展,因此現(xiàn)在的設計能夠支持可能出現(xiàn)的新的語音算法或標準是非常重要的。

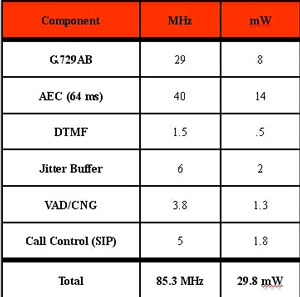

這些算法的處理傳統(tǒng)上都是在雙內核系統(tǒng)上進行的,系統(tǒng)中的通用處理器用于控制和管理功能,DSP內核用于語音編解碼和高質量的算法處理。如表1所示的頻率評估那樣,如今整合了RISC和DSP功能的嵌入式處理器足夠為全雙工通道提供執(zhí)行這些運算所需的帶寬。雖然每個架構實現(xiàn)DSP功能的方式不同,因此處理語音算法的效率有高有低,但是設計師可以采用一種通用規(guī)則,即一個全雙工通道使用約100MHz的帶寬或100MCPS(每秒百萬周期)。在DSP性能得到增強的RISC內核上,這個帶寬一般占總的可用帶寬的一半以下,因此能給大多數(shù)VoIP設備預留出足夠的應用余量。

語音處理對單內核系統(tǒng)僅僅增加30到60mW的功耗。功率由動態(tài)功率和靜態(tài)功率組成(P=CV2F+IV),每個通道語音數(shù)據(jù)的處理和傳送的功率用動態(tài)功耗的頻率分量來表示,并且動態(tài)功耗的大小取決于處理器的功率模式和CPU內核執(zhí)行特定算法所需的周期數(shù)。大多數(shù)供應商都能提供特定半導體工藝的常規(guī)處理器的每兆赫茲功耗估計,CPU處理算法所需的周期數(shù)很大程度上取決于處理器的DSP功能的執(zhí)行效率和算法代碼的優(yōu)化程度。表1給出了基于ARM9E(臺積電的0.13微米工藝)內核的高度優(yōu)化解決方案的估算功耗,該值處于功耗范圍的下限-更低效率的內核只會導致更高的功耗。

語音處理給單內核系統(tǒng)增加30到60mW的功耗,而傳統(tǒng)的雙內核系統(tǒng)增加的功耗可能是這個數(shù)字的二到三倍。DSP內核和存儲器系統(tǒng)不僅在時鐘信號驅動下會產(chǎn)生動態(tài)功耗,由于第二個子系統(tǒng)而需要增加的門電路還會消耗額外的靜態(tài)功耗。

SoC設計師可以采用在單處理器上結合了控制和信號處理功能的單內核架構降低功耗和成本。使用一個CPU的方法可以簡化設計、減少整合問題、縮短開發(fā)時間并降低風險,同時還能減少芯片周邊的數(shù)據(jù)傳輸。將語音劃分給CPU處理意味著只有一個存儲器系統(tǒng),分立DSP的劃分方案涉及多個存儲器系統(tǒng),以及DSP和CPU內核之間的包交換,而占用的每個時鐘周期都要消耗功率。除了降低功耗外,給CPU增加數(shù)據(jù)層功能可以降低開發(fā)和產(chǎn)品成本。使用單個工具鏈而非分離的DSP和CPU的軟件開發(fā)可以在工具和工時數(shù)方面減少設計費用。此外,采用一個內核而不是兩個內核可以減少內核和存儲器系統(tǒng)的裸片面積,從而降低裸片的成本。單內核可降低總體擁有成本:一個IP授權引起的法律費用、維護費用、版稅和許可費用都要少很多。

RISC+DSP

通用的嵌入式RISC處理器在20世紀90年代后期開始集成數(shù)字信號處理功能。像ARM9E處理器中的增強的DSP功能就是代DSP功能,它支持快速和靈活的16×16MAC與飽和算法。這個創(chuàng)新性設計對語音和音頻處理很理想,因為這種處理需要組合的數(shù)字信號處理和控制功能。在某些情況下,新的DSP指令專門針對于處理16位語音數(shù)據(jù)所需的常見的循環(huán)(loop)。例如,ITU規(guī)定的許多語音算法要求在每次操作后進行溢出/飽和校驗。用于加法和減法指令的飽和擴展減少了周期數(shù),并降低了功耗,顯著地減少了指令數(shù)量。其它有益于語音處理的新增功能包括用于改進的歸一化和靈活的寄存器尋址的CLZ(前導零計數(shù))指令,與以前的RISC架構相比,其數(shù)據(jù)和系數(shù)值加載和存儲效率會更高。這些新增功能進一步減少了資源使用和周期數(shù)量。

除了使性能相對于獨立的RISC架構提高了二到三倍,這些擴展還可以讓設計師重新劃分他們的設計。在諸如需要支持1至2路語音通道的手機這樣的應用中,不再需要增加單獨的DSP內核或語音處理加速器。去掉第二個DSP內核可以減少門電路數(shù)量和簡化設計過程,由此可以使成本下降多達40%。

后續(xù)的幾代處理器(如ARM11)集成了更復雜的信號處理邏輯和指令,可進一步提升那些需要中等或高復雜度的信號處理應用的性能。在幾種嵌入式處理器中還集成了SIMD(單指令多數(shù)據(jù))引擎,配合新的指令可以充分發(fā)揮視頻和多媒體處理算法的固有并行處理優(yōu)勢。這些架構還改善了語音處理性能,相比DSP增強的內核速度提升20-30%。因此這些內核非常適用于二個以上通道的應用,如家庭網(wǎng)關或同時支持視頻和語音的應用。這些架構一般有更長的流水線,因此可以工作在更高的頻率。由于這些內核有更大的帶寬,因此可以支持更大的應用負載。然而性能的增加自然也要增加裸片和功率成本,設計師必須仔細斟酌產(chǎn)品的使用情況和應用的性能需求,力求做到處理需求與性能一致。

評估DSP功能

在評估某個特定內核的DSP功能時需要考慮架構的性能和效率以及對架構的支持。在判斷你的應用負載能否被單一處理器支持時,性能是至關重要的條件。另外,RISC處理器的DSP性能將影響語音處理時消耗的功率。對特定內核DSP功能的評估是采用實際的代碼和硅片進行,但考慮到需要在開發(fā)開始之前評估性能,某些基準測試程序可能會對決策制定的過程提供幫助。可以采用專注于數(shù)字信號處理的基準測試,如伯克利設計科技有限公司(BDTI)發(fā)布的BDTIBenchmarks分析內核的DSP性能。在為了優(yōu)化性能而將算法調整到適合架構的應用(比如語音處理)中,BDTIBenchmarks可以對在一般信號處理應用中手工調整的匯編代碼例程的性能提供指導。BDTI的結果可以幫助設計師以一定的精度預測該類型的代碼在特定處理器上運行的情況。RISC處理器的DSP功能在性能上的微小差別反映到功耗上差別就可能變得很大。裸片大小和存儲器效率是第二個關鍵問題,因為性能的提高可能以效率作為代價。

在處理器性能給定的情況下,內核大小比較的結果怎樣?增加的性能應該用的硅片成本實現(xiàn)。,由于上市時間周期越來越短,利潤空間的壓力越來越大,內核擴展得到大量工具、OS和中間件供應商的支持是非常重要的,是否具備用于軟DSP解決方案的高度優(yōu)化的語音處理軟件是非常重要的考慮因素。用匯編編寫、手工優(yōu)化的用于特定處理器的優(yōu)化軟件對保持足夠的應用負載余量非常重要。未經(jīng)優(yōu)化的解決方案速度可能會下降高達40%,和/或使用顯著增多的存儲器。從DSP指令的恰當使用到消除了不必要的指令和并行機制的流水線,這些供應商在算法調整和語音框架軟件方面都非常專業(yè)。軟件提供的這些特性有助于實現(xiàn)具有競爭力的解決方案,并釋放出寶貴的工程資源專門用于產(chǎn)品的差異化開發(fā)。大多數(shù)軟件供應商可以提供在不同嵌入式處理器平臺上優(yōu)化的解決方案所需的周期數(shù)和存儲器的詳細統(tǒng)計數(shù)據(jù),從而在設計過程早期就向設計師和系統(tǒng)集成商提出硬性的目標要求。

本文小結

借助于支持軟DSP架構的現(xiàn)成的軟件解決方案,具有DSP功能的RISC處理器提供的一體化軟件包,能滿足對功耗和成本都很敏感的設計的需求。在單個設備中融合很多應用功能的今天,具有DSP功能的嵌入式RISC處理器可以在不增加系統(tǒng)復雜性、對功耗影響很小的前提下,為這些新增功能提供很好的解決方案。設計師真的可以“少勞多得”,通過在一個處理器中集成多項功能來優(yōu)化系統(tǒng)的成本和功耗。在不遠的將來,這種設計劃分方案將生產(chǎn)出低于100美元價格門檻要求的高能效手機,實現(xiàn)視頻和VoIP設備,并將VoIP移植到原本沒有語音功能的設備上,比如打印機或便攜式媒體播放器。這些功能強大、節(jié)省成本的解決方案的出現(xiàn)將推動VoIP的應用。